# Chorale

### Chorale Reduces Schedule and Technology Risks for Chipset Suppliers

The combination of Dynamic Spectrum Management (DSM) and vectored DSL will deliver DSL speeds in excess of 100 Mbps, enabling DSL to effectively compete with other broadband delivery mechanisms for the foreseeable future. Operator interest in DSM and vectored DSL is growing, further stimulated by the publication of the ATIS DSM Report and new ITU-T initiatives to standardize vectored DSL.

Vectored DSL presents significant new challenges for DSL modem chipset manufacturers. Vectoring is computationally intensive. It requires new architectures with increased processing capabilities, new signal processing algorithms, and substantially different dataflow characteristics as compared to traditional unvectored systems. An interface to a Spectrum Management Center (SMC) that coordinates the vectoring process is another new necessary component.

The ASSIA® Chorale® product reduces schedule and technology risk for chipset vendors developing vectored DSL solutions. The product includes the following components.

- Best-in-class algorithms and simulation tools for modem development

- Chorale SMC interface specifications for vectoring and DSM

- 400 hours of implementation and validation consulting from ASSIA developers

- Chorale SMC interface certification

- Licenses to all of ASSIA's patents necessary to build and deliver vectored DSL chipsets

The Chorale product builds on ASSIA's Rapide® product, and incorporates all Rapide features for DSM Levels I and II including loop diagnostics interfaces.

World-class,

### **Vectored DSL**

development package

includes expert

assistance and

technology

licensing.

### **Chorale Components**

#### LINK LEVEL SIMULATOR

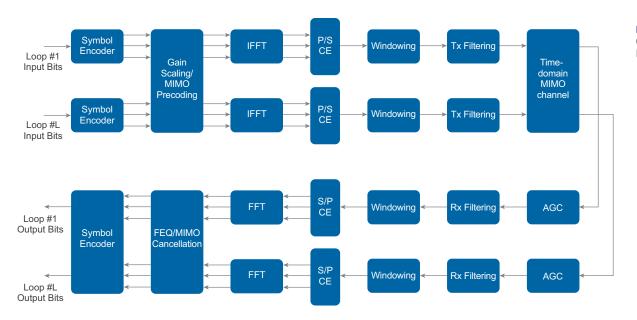

The Chorale link level simulator, shown in Figure 1 is a complete baseband symbol-level simulator for vectored DSL systems incorporating multiple loops and a MIMO channel.

The simulator is implemented in MATLAB® from MathWorks® with CMEX accelerators for the computationally intensive operations. Fixed point simulation of numerically sensitive operations aids designers in word sizing for hardware design and in the generation of test vectors for design and product validation.

## FIGURE 1. Chorale Link Level Simulator

#### **VECTORING ALGORITHMS**

ASSIA's developers have been at the forefront of DSL and vectoring technology since its inception and include the original Stanford University developers of the concept. Chorale's vectoring algorithms have been optimized for performance, for numerical stability, and for efficient execution in the hard real-time application of vectored DSL baseband processing.

As each chipset vendor is expected to have a different processing architecture with its own unique features and objectives, the Chorale package includes ASSIA consulting services that can be applied to adapt the Chorale vectoring algorithms to a particular platform.

### CHORALE SMC INTERFACE SPECIFICATIONS

The SMC provides an upper layer of intelligence in a vectoring system, identifying mutually interfering groups of lines on a tone-by-tone basis. This information is used to configure signal routing, via either cross-connect switches or on-chip routing, that couples lines with strong mutual interference to a single vectoring engine and to configure the vectoring algorithms. The Chorale SMC interface specification defines a complete communications protocol for the exchange of DSM III information between the DSLAM modems and the SMC.

The SMC interface specification also defines a protocol between the DSLAM modems and the SMC for line diagnostics and for line profile management including INP, noise margins, retraining thresholds, power management, and other key DSL

operating parameters. The high value of these management interfaces to carriers with SMCs has been repeatedly demonstrated in carrier deployments and field trials.

#### **CONSULTING**

ASSIA's Chorale product includes 400 hours of consulting from key ASSIA personnel in the areas of vectoring algorithms, chipset design, and Chorale interface certification. ASSIA's DSL experience and insight greatly increase the speed of development and validation processes through the elimination of false starts and accurate root cause analysis for problem areas.

#### **CHORALE CERTIFICATION**

Successful completion of the Chorale product development process concludes with Chorale interface certification.

Certification is awarded upon successful completion of the Chorale test suite.

ASSIA personnel assist throughout the test process, participating in testing, validating test results, and working with the customer to resolve any implementation issues uncovered by the testing.

#### **LICENSES**

The Chorale product includes licenses to all IP owned or controlled by ASSIA, including certain patents owned by Stanford University, that is necessary to implement the Chorale SMC interface specification and ASSIA-supplied vectoring algorithms.

Interested in reducing development time and costs associated with vectored DSL chipsets?

Contact ASSIA today at +1.650.654.3400 or send an email to sales@assia-inc.com

333 Twin Dolphin Drive Redwood City, CA 94065 Telephone: +1-650-654-3400 Fax: +1-650-654-3404 www.assia-inc.com

© 2011 ASSIA, Incorporated. All rights reserved.

ASSIA, the ASSIA logo, Chorale, and Rapide are registered trademarks of ASSIA, Incorporated. All other product names, company names, logos, and trademarks are used herein for identification purposes only and are the property of their respective companies.

Rev 102010 P/N MC-CH-0110-01-00